The MASTECS project, (Multicore Analysis Service and Tools for Embedded Critical Systems) has developed the first certification-ready timing analysis solution capable of handling the complexity of safety-critical multicore systems. The technology developed and consolidated within the project is now enabling the use of multicore processors in aerospace and automotive domains.

MASTECS has enabled the partners to mature their multicore timing analysis technology, from Technology Readiness Level (TRL) 6 to 8 and bringing it to market.

The project helped to develop tools and methods that support both the avionics and automotive domains, which both have a strong focus on applicable safety standards and emerging certification requirements.

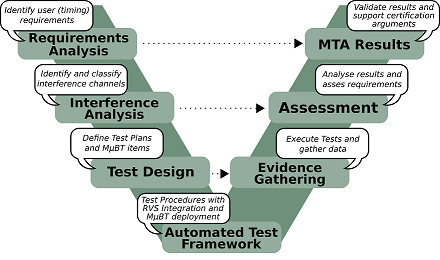

The multicore timing analysis workflow builds on the use of specialized micro-benchmarks that create interference on multicore processors and demonstrate the possible effect that such interference can have on software.

The workflow also features a task contention model that provides early estimates of the contention delay suffered by tasks. A 7-step design methodology was also developed to fully understand and characterize the impact of interference on timing behaviour (see below).

The MASTECS project helped to develop a clear methodology for meeting the safety certification requirements in aerospace and automotive using multicore processors for advanced software functions, supporting wider benefits such as:

- Improving safety in the automotive and avionics domains,

- CO2 profile reduction for different types of vehicles,

- New flight technologies, including personal air vehicles making commercial flights and further mobility solutions accessible.

A fruitful pathway

After two years of progress, despite the challenges encountered due to the COVID-19 outbreak, MASTECS had many major achievements:

- New commercial technologies brought to the market including (CAST-32 Compliance Solution for aerospace, Multicore Timing Solution for other markets), generating sustainable and growing revenue for EU/UK industry.

- Creation of the new spinoff company Maspatechnologies to commercialize interference generator technology.

- New high-tech jobs.

- Increased capability of all partners: new tools, new technologies, a new understanding of building reliable systems on multicore processors.

“Despite the pandemic, MASTECS has accomplished its objective of maturing the multicore technology to a state that is now commercially available. This will bring huge benefits to EU companies in domains like avionics and automotive by helping them to adopt multicore processors in their products” says Francisco J. Cazorla, MASTECS Project Coordinator and Operating System group manager at the Barcelona Supercomputing Center (BSC).

The MASTECS technology has been evaluated and proven by case studies. These included the use of the technology in Civil Certified Vehicle Management Computer provided by Collins Aerospace Applied Research & Technology (Collins ART) and analysis of a Vehicle Domain Control Module (VDCM) by Marelli Europe, in the avionics and automotive domains respectively.

Press release in PDF