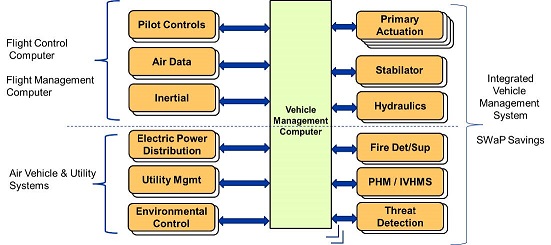

Collins Aerospace, a unit of Raytheon Technologies Corp. (NYSE: RTX), is a leader in technologically advanced and intelligent solutions for the global aerospace and defense industry. Created in 2018 by bringing together UTC Aerospace Systems and Rockwell Collins, Collins Aerospace has the capabilities, comprehensive portfolio, and expertise to solve customers' toughest challenges and to meet the demands of a rapidly evolving global market. From the Research Centre of Raytheon Technologies in Ireland (former United Technologies), we are demonstrating the use of the MASTECS technology for the Civil Certified Vehicle Management computer. This is an adaptable baseline DAL-A (flight-critical) vehicle management computer able to host 3rd party applications, see Figure 1, combining existing legacy parts of Collins Aerospace Flight Control systems.

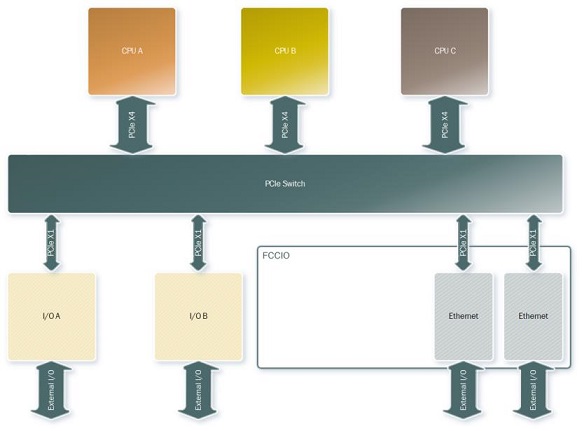

The system is compatible with the RTCA DO-297 standard for integrated modular avionics; it includes customer configurable I/O, scalable redundancy, cybersecurity protections, etc. The system contains triplex dissimilar high-performance processors as seen in Figure 2. The MASTECS project will be focused on the analysis of the software architecture running in one of these processors, the NXP T2080 quad core processor.

The system includes all necessary functions for flight-critical fly-by-wire system:

• All I/O has an Enable/Disable capability at the circuit level

• Watchdog Timers (WDT), Clock Monitors, Activity Monitors

• Cross Channel Data Links

• Cross Channel Status

• Internal Lane-to-Lane Synchronization

• External Channel-to-Channel Synchronization

• Multiple Sources of 28 VDC power

• Power hold-up circuitry

• Extensive Built-In Test (BIT)

The draft architecture of the system can be seen in Figure 2. Each Channel contains different subsystems or lanes. The idea is to offer two levels of redundancy, having different channels per aircraft and triplicated processing units per lane.

As it can be seen in Figure 2, the VMC architecture includes 6 functional components within the same integration unit that are connected via a PCIe switch:

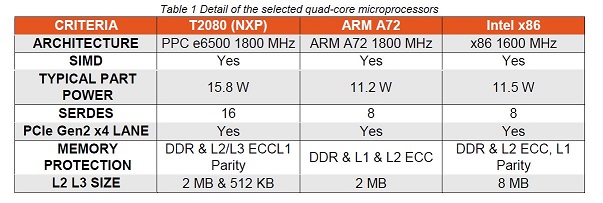

• Three dissimilar quad core SBC processing units; a NXP T2080 processor, an Intel x86 processor, and an ARM A72 based processor. Table 1 shows detailed information of the processing units included.

• One FCC I/O Card: used for Ethernet data link and synchronization purposes.

• Two I/O Processor Cards: used for analog & discrete I/O communication with external devices.

The integration and timing analysis of such a system, with the added difficulty of hosting 3rd party applications, is extremely challenging. Guaranteeing deterministic Worst-Case Execution Time (WCET) values is very difficult and requires extensive hardware and software knowledge together with extremely thorough testing processes. The purpose of the MASTECS project is to achieve not only that but this analysis in a much shorter time when compared to the state of the art.

Approved for Public Release